## **TECHNICAL MANUAL**

# OPERATOR'S, ORGANIZATIONAL, DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE (INCLUDING REPAIR PARTS AND SPECIAL TOOLS LISTS) FOR DATA ANALYZER DA-404 (STELMA MODEL DA-404)

HEADQUARTERS, DEPARTMENT OF THE ARMY

**15 OCTOBER 1980**

#### WARNING

Adequate ventilation should be provided while using TRICHLOROTRIFLUOROETHANE. Prolonged breathing of vapor should be avoided. The solvent should not be used near heat or open flame; the products of decomposition are toxic and irritating. Since TRICHLOROTRIFLUOROETHANE dissolves natural oils, prolonged contact with skin should be avoided. When necessary, use gloves which the solvent cannot penetrate. If the solvent is taken internally, consult a physician immediately.

#### CAUTION

Do not make more than one input connection at a time. Use only the appropriate input jack, and leave the other input jack unconnected.

#### NOTE

Do not destroy or discard the packing case. It can be used when reshipping the unit to the manufacturer or repair facility in case of equipment damage or malfunction.

This manual contains copyright material reproduced by permission of Stelma, Incorporated

No. 11-6625-2815-14&P

HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, DC, *15 October 1980*

#### OPERATOR'S, ORGANIZATIONAL, DIRECT SUPPORT, AND GENERAL SUPPORT MAINTENANCE (INCLUDING REPAIR PARTS AND SPECIAL TOOLS LIST) FOR

## DATA ANALYZER DA-404 (STELMA MODEL DA-4) Current as of 30 May 1980

#### **REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS**

You can help improve this manual. If you find any mistakes or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended Changes to Publications and Blanks Forms), or DA Form 2028-2 located in back of this manual direct to: Commander, US Army Communications and Electronics Materiel Readiness Command, ATTN: DRSEL-ME-MQ, Fort Monmouth, NJ 07703.

In either case, a reply will be furnished direct to you.

#### TABLE OF CONTENTS

|         |      |                                                              | Page |

|---------|------|--------------------------------------------------------------|------|

| Section | Ο.   | INSTRUCTION                                                  | 0-1  |

|         |      | 0-1. Scope                                                   | 0-1  |

|         |      | 0-2. Indexes of Publications                                 | 0-1  |

|         |      | 0-3. Maintenance Forms, Records, and Reports                 | 0-1  |

|         |      | 0-4. Reporting Equipment Improvement Recommendations (EIR)   | 0-1  |

|         |      | 0-5. Administrative Storage                                  | 0-1  |

|         |      | 0-6. Destruction of Army Electronics Materiel                | 0-1  |

|         | ١.   | INTRODUCTION                                                 |      |

|         |      | 1-1. Data Analyzer                                           | 1-1  |

|         |      | 1-2. Description                                             | 1-1  |

|         |      | 1-3. Preparation for Use                                     | 1-2  |

|         | II.  | OPERATION                                                    |      |

|         |      | 2-1. Operating the Data Analyzer                             | 2-1  |

|         |      | 2-2. Preliminary Setup                                       | 2-2  |

|         |      | 2-3. Operating Procedures                                    | 2-2  |

|         |      | 2-4. Interpreting Indications                                | 2-2  |

|         |      | 2-5. Operational Condition                                   | 2-3  |

|         |      | 2-6. Battery Charging Procedure                              | 2-3  |

|         | III. | PRINCIPLES OF OPERATION                                      |      |

|         |      | 3-1. Overall Functional Description                          | 3-1  |

|         |      | 3-2. General                                                 | 3-1  |

|         |      | 3-3. Input Circuits, Functional Description                  | 3-1  |

|         |      | 3-4. Timing and Control Circuit, Functional Description      | 3-3  |

|         |      | 3-5. Distortion Measurement Circuits, Functional Description | 3-5  |

|         |      | 3-6. Output Circuits, Functional Description                 | 3-7  |

|         |      | 3-7. Discrete Component CircuitDetailed Description          | 3-8  |

|         |      | 3-8. Power Supply Inverter                                   | 3-9  |

|         |      | 3-9. Battery Test Circuit                                    | 3-9  |

|         | IV.  | MAINTENANCE                                                  |      |

|         |      | 4-1. Maintenance Practices                                   | 4-1  |

|         |      | 4-2. Test Equipment Required                                 | 4-1  |

|         |      | 4-3. Performance Test                                        | 4-1  |

|         |      | 4-4. Repair                                                  | 4-4  |

|         |      | 4-5. Time Base (Oscillator Frequency Adjustment              | 4-5  |

|         |      | 4-6. Strapping Options                                       | 4-5  |

|         | ۷.   | PARTS LIST                                                   |      |

|         |      | General                                                      | 5-1  |

|         | VI.  | PART NUMBER-NATIONAL STOCK NUMBER CROSS REFERENCE INDEX      | 6-1  |

|          |      |                                                                | Page |

|----------|------|----------------------------------------------------------------|------|

| APPENDIX | Α.   | REFERENCES                                                     | A-1  |

|          | В.   | COMPONENTS OF END ITEM LIST (Not applicable)                   |      |

|          | C.   | ADDITIONAL AUTHORIZATION LIST(Not applicable)                  |      |

|          | D.   | MAINTENANCE ALLOCATION                                         |      |

| Section  | Ι.   | Introduction                                                   | D-1  |

|          | II.  | Maintenance Allocation Chart for Data Analyzer DA-404A         | D-3  |

|          | III. | Tool and Test Equipment Requirements for data analyzer DA-404A | D-4  |

| APPENDIX | Ε.   | EXPENDABLE SUPPLIES AND MATERIALS LIST(Not applicable)         |      |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------------|------|

| 1-1    | Data Analyzer, ModelDA-404                                                                   | 0-2  |

| 2-1    | Data Analyzer, Front, Top, Back Views                                                        | 1-3  |

| 2-2    | Typical Percent Distortion Readout                                                           | 2-2  |

| 2-3    | Examples of Bias and End Distortion                                                          | 2-3  |

| 3-1    | Data Analyzer, Block Diagram                                                                 | 3-2  |

| 3-2    | Data Analyzer, Timing Diagram                                                                | 3-4  |

| 3-3    | Mark/Space Indicator Control Timing Diagram                                                  | 3-9  |

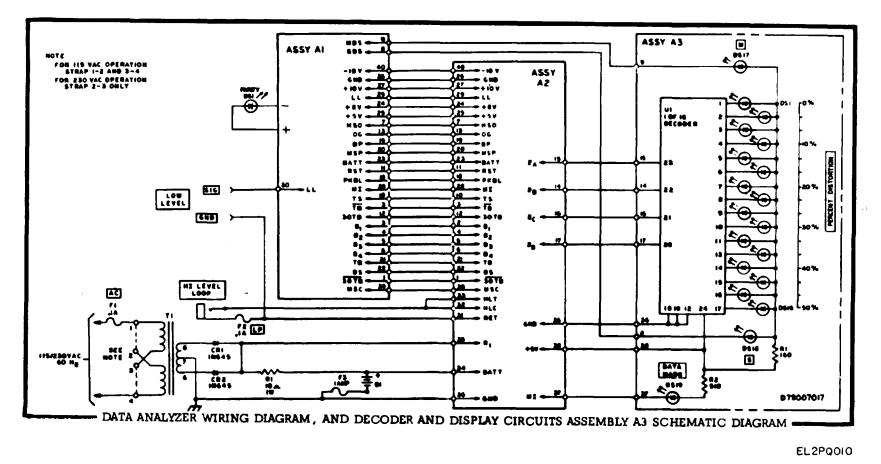

| 4-1    | Data Analyzer Wiring Diagram, and Decoder and Display Circuits Assembly A3 Schematic Diagram | 4-2  |

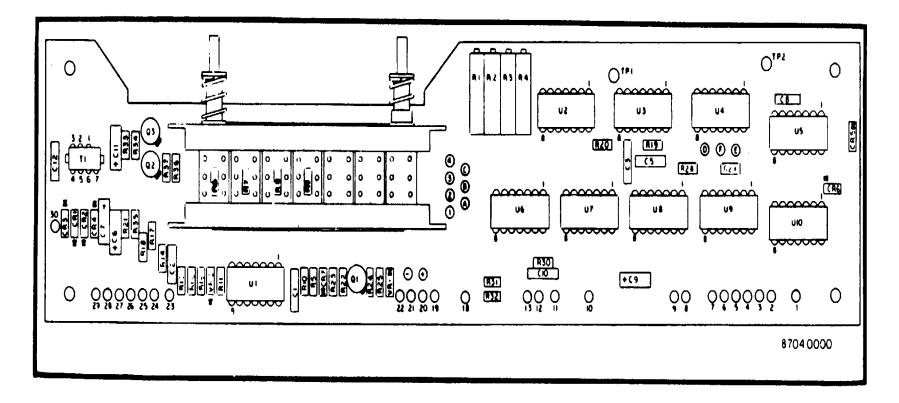

| 4-2    | Tuning, Parity, and Power Assembly AI, Component Location Diagram                            | 4-6  |

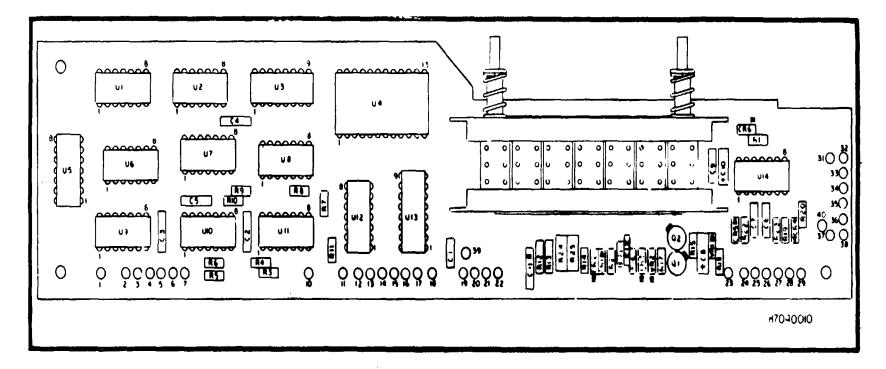

| 4-3    | Distortion Measuring Circuit Assembly A2, Component Location Diagram                         | 4-7  |

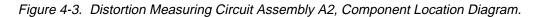

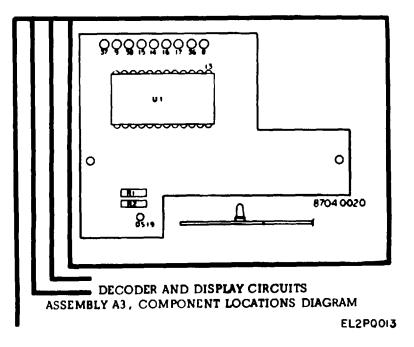

| 4-4    | Decoder and Display Circuit Assembly A3, Component Locations Diagram                         | 4-8  |

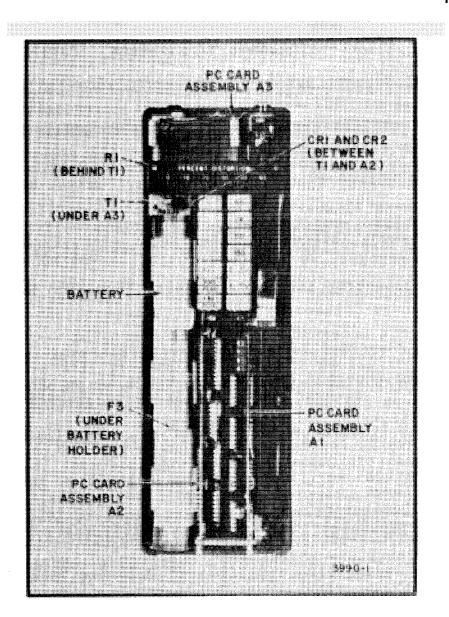

| 4-5    | Data Analyzer Top View, Component Locations                                                  | 4-9  |

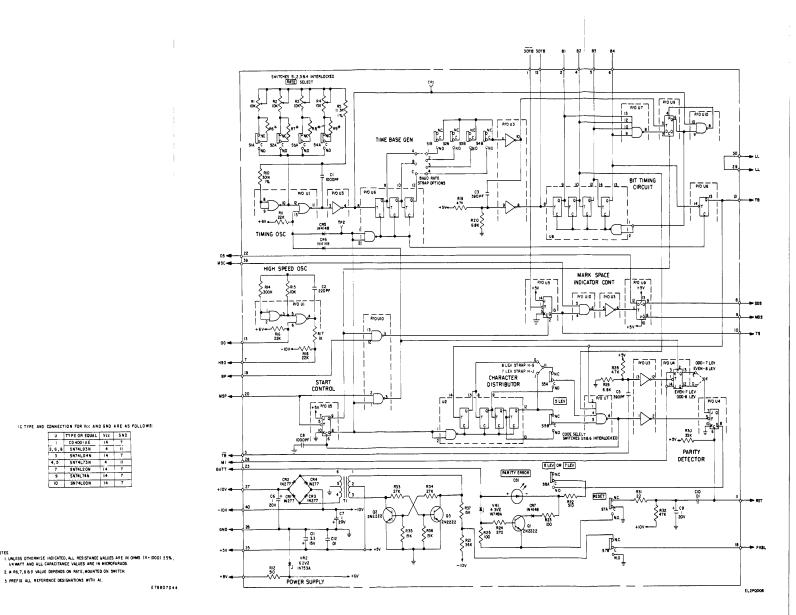

| FO-1   | Timing, Parity, and Power Assembly AI, Schematic Diagram                                     | FO-1 |

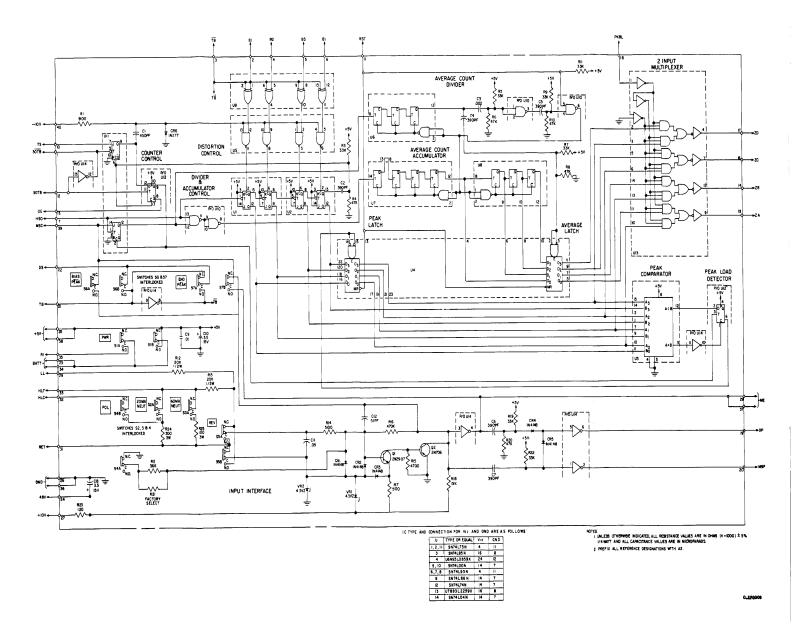

| FO-2   | Distortion Measuring Circuits Assembly A2, Schematic Diagram                                 | FO-2 |

#### LIST OF TABLES Number Title Page' 1-1 Technical Specifications 1-2 2-1 Controls, Indicators, Jacks, Fuses ..... 2-1 4-1 Test Equipment Required ..... 4-1 4-2 4-3 Performance Test ..... 5-1 Manufacturer Codes ..... 5-1 5-2 5-1 Replaceable Parts

This manual is an authentication of the manufacturer's commercial literature which, through usage, has been found to cover the data required to operate and maintain this equipment. Since the manual has not been prepared in accordance with military specifications and AR 310-3, the format has not been structured to consider level of maintenance.

ii

#### **SECTION O**

#### INSTRUCTION

#### 0-1. SCOPE

This manual describes Data Analyzer, Stelma Model DA-404, and provides instructions for operation, maintenance, and performance testing. Throughout this manual, the DA-404 is referred to as Data Analyzer.

#### 0-2. INDEXES OF PUBLICATIONS

a. DA Pam 310-4. Refer to the latest issue of DA Pam 310-4 to determine whether there are new editions, changes, or additional publications pertaining to the equipment.

*b. DA Pam 310-7.* Refer to DA Pam 310-7 to determine whether there are modification work orders (MWO's) pertaining to the equipment.

# 0-3. MAINTENANCE FORMS, RECORDS, AND REPORTS

a. Reports of Maintenance and Unsatisfactory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by TM 38-750, The Army Maintenance Management System.

*b. Report of Packaging and Handling Deficiencies.* Fill out and forward DD Form 6 (Packaging Improvement Report) as prescribed in AR 735-11-2/NAVSUPINST 4440.127E/AFR 400-54/MCO 4430.3E and DSAR 4140.55.

c. Discrepancy in Shipment Report (DISREP) (SF

*361). Fill* out and forward Discrepancy in Shipment Report (DISREP) (SF 361) as prescribed in AR 55-38/NAVSUPINST 4610.33B/AFR 75-18/MCO P4610.19C and DLAR 4500.15.

#### 0-4. REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR)

If your Data Analyzer, Stelma Model DA-404, needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design. Tell us why a procedure is hard to perform. Put it on an SF 368 (Quality Deficiency Report). Mail it to Commander, US Army Communications and Electronics Materiel Readiness Command, ATIN: DRSEL-ME-MQ, Fort Monmouth, New Jersey 07703. Well send you a reply.

#### 0-5. ADMINISTRATIVE STORAGE

Administrative storage of equipment issued to and used by Army activities shall be in accordance with paragraph 5-5.

#### 0-6. DESTRUCTION OF ARMY ELECTRONICS MATERIEL

Destruction of Army electronics materiel to prevent enemy use shall be in accordance with TM 750-244-2.

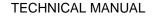

Figure 1-1. Data Analyzer, Model DA-404.

#### SECTION I

#### INTRODUCTION

#### 1-1. DATA ANALYZER

a. Data Products' Data Analyzer DA-404 (fig. 1-1) is a compact, portable, ac/battery operated test set that measures and indicates the type and magnitude of distortion present in all characters of start stop (asynchronous) data/telegraph signals; the monitored signal may be 5-level, and either 7-level or 8-level code (strap selectable)-using low-level polar : 3 to :25 volts, high-level polar (10 to 30ma), or neutral (20 or 60ma) inputs. The unit also indicates the presence of detected parity errors in 7- or 8-level coded data signals.

b. Measurements may be made at any one of four customer specified, standard baud-rates, ranging from 37.5 to 300 bauds. While measuring end or bias distortion (Marking or Spacing), the Data Analyzer also simultaneously indicates total peak distortion present in the signal. Used with an associated test pattern generator (such as Pattern Generator, Data Products' Model PG-404), the Data Analyzer provides a comprehensive field capability for testing and evaluating the performance of data/telegraph systems and equipment.

#### **1-2. DESCRIPTION**

a. Basically, the Data Analyzer comprises four principal sections: distortion measurement circuit, parity error detector, input circuits, and power supply.

(1) Distortion Measurement Circuits. The Data Analyzer measures both of the following types of asynchronous signal degradations:

- (a) Average bias and total peak distortion.

- (b) Average end and total peak distortion.

#### NOTE

Peak distortion readouts can be either bias or end distortion, whichever is higher.

(2) Bias or end distortion, as well as peak distortion readouts are simultaneously displayed on a solid-state meter, using light emitting diodes (LEDs) mounted behind a smoked plexiglass panel. The panel is marked in graduations of percent distortion, from 0 to 50, in 3-1/3 percent increments. When measuring bias or end distortion, the sense (Marking or Spacing) of the detected distortion is displayed by two LED indicators. Peak distortion measurement may be reset by depressing a front-panel pushbutton.

(3) Parity Error Detector. The unit detects and indicates odd- or even- (strap selectable) parity errors in

7-level or 8-level coded signals. The parity error indicator may be reset, by means of the same pushbutton that resets the peak distortion indicator.

(4) Input Circuits. The Data Analyzer accommodates three types of data/telegraph input signal:

(a) Low-level logic (t 3 to t 25 volts) that, by means of a front-panel polarity-reversing (POLARITY REV) switch, may be made to conform with EIA Standard RS-232B (negative Mark) or MIL-MTD-188B (positive Mark).

(b) High-level neutral loops (20 or 6(mn).

#### NOTE

Through the use of the POLARITY REV switch, neutral input loops can be wired with either positive or negative jack tips.

(c) High-level polar loops (10 to 30ma).

(5) Power Supply. Data Analyzer d operating voltages are supplied by an inverter circuit powered by: (1) an internal, rechargeable 5 volt battery (during battery operation); or (2) a full-wave power supply (during ac operation). Recharging current *is* supplied to the battery when the ac line cord is connected to a 115-volt or 230-volt (strap selectable), 60Hz power source. Battery recharging occurs when the front-panel PWR switch is off (heavy charge), or when the equipment is operating (trickle charge). The battery condition may be checked by means of a front-panel pushbutton and indicator lamp.

b. As shown in figure 1-1, the Data Analyzer is contained in a 2-piece, molded plastic carrying case provided with a fold-away handle. All operating controls and indicators, located on the top panel, are protected by a sliding aluminum cover; when open, the sliding cover permits access to the ac line cord storage compartment in the side of the unit. Input signal connections are made at jacks on the front panel; ac power and loop fuses are recessed in the bottom of the unit.

c. Al Data Analyzer electronics are solid-state-including integrated circuits (ICs) and, except for the power transformer and batteries, are constructed on three printed circuit (PC) cards (Assemblies Al, A2, and A3). For access to internal components for maintenance and repair, as required, the upper portion of the carrying case may easily be removed. Table 1-1. Technical Specifications

| Item                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT SIGNAL:<br>Speeds<br>Mode<br>Format<br>Levels<br>compatible.<br>Impedance<br>Polarity | Any standard four customer-specified (strap selectable) rates from 37.5 to 300 bauds.<br>Start-stop (asynchronous).<br>5-level, and either 7-level or 8-level code.<br>20/60ma neutral; 10 to 30ma (high-level) polar; t 3- to + 25-volt (low-level) polar, RS-232B/MIL-STD-188B<br>100 ohms, 60ma loop; 300 ohms, 20ma loop; 25,000 ohms, low-level input.<br>Selectable by front-panel switch. |

| DISTORTION<br>MEASUREMENT:<br>Types<br>Range<br>Accuracy                                    | <ul> <li>Bias or end distortion, and simultaneous peak distortion. (Peak distortion readout may be either bias or end peak, whichever is higher.)</li> <li>0 to 50 per cent, in 3-1/3 percent increments.</li> <li>3-113 percent.</li> </ul>                                                                                                                                                     |

| PARITY<br>MEASUREMENT                                                                       | Odd or even parity (strap selectable) for 7- or 8-level codes.                                                                                                                                                                                                                                                                                                                                   |

| PARITY ERROR                                                                                | Lamp indicates parity error (odd or even, strap selectable); indicator lamp is reset by front-panel pushbutton.                                                                                                                                                                                                                                                                                  |

| OPERATING MODES                                                                             | Ac or battery.                                                                                                                                                                                                                                                                                                                                                                                   |

| BATTERY MODE<br>OPERATING TIME                                                              | More than 12 hours of continuous operation, with fully charged battery.                                                                                                                                                                                                                                                                                                                          |

| BATTERY CHARGING<br>TIME                                                                    | 16 hours (approximate) from full-discharge to full-charge condition, with power OFF; unit may be operated while battery is being recharged (trickle charge).                                                                                                                                                                                                                                     |

| POWER<br>REQUIREMENTS:<br>Ac<br>Battery                                                     | 115 or 230 volts (strap selectable), 60 Hz.<br>6 volts, rechargeable NICD.                                                                                                                                                                                                                                                                                                                       |

| DIMENSIONS<br>(inches)                                                                      | 3-13/16 wide, 11-112 high, 3-5/8 deep.                                                                                                                                                                                                                                                                                                                                                           |

| WEIGHT(pounds)                                                                              | 3-1/2.                                                                                                                                                                                                                                                                                                                                                                                           |

#### **1-3. PREPARATION FOR USE**

a. Unpacking.

(1) When shipped from the factory, the Data Analyzer has all customer-specified wiring options installed so that it may be placed into operation immediately after it has been unpacked.

(2) Remove the Data Analyzer from its packing case, and carefully check for damage that may have occurred during shipment. Immediately notify the carrier and/or the manufacturer of any damage to the equipment.

#### NOTE

Do not destroy or discard the packing case. It can be used when reshipping the unit to the manufacturer or repair facility in case of equipment damage or malfunction.

b. Electrical Connections.

(1) Use of the Data Analyzer with low-level, highlevel polar, or neutral loop circuits requires that proper external connections be made to the front-panel jacks. Particular applications may require that certain customerspecified factory wired strapping connections be changed; the Data Analyzer contains strapping terminals for such alternate configurations, to satisfy requirements of different system applications and uses. Refer to paragraph 4-6 for a description of the various strapping options.

(2) Input jacks for high-level (neutral or polar) and low-level (polar) signals are located on the unit's front panel. The input jacks to be used depend on the type of circuit being tested.

(a) Use a Western Electric plug Type 347 (or equivalent) for connections to the HI LEVEL LOOP jack; once this connection is made, select either high-level polar or neutral loop monitoring by means of the push buttons at the unit's top panel.

(b) Use a Pomona type MDP dual banana plug (or equivalent) for connections to the LOW LEVEL jacks.

#### CAUTION

Do not make more than one input connection at a time. Use only the appropriate input jack, and leave the other input jack unconnected.

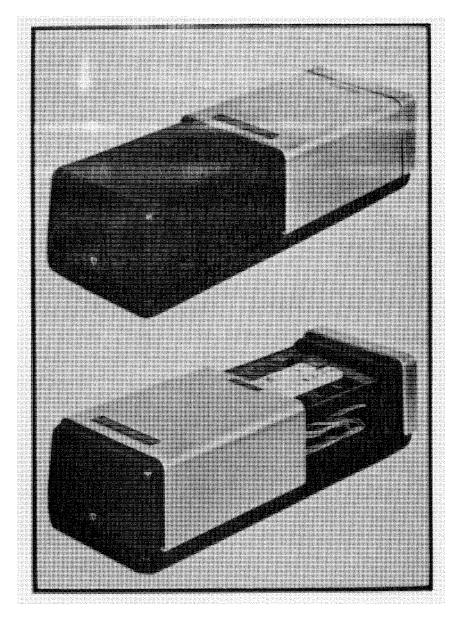

Figure 2-1. Data Analyzer-front, top, back views.

### **SECTION II**

#### **OPERATION**

### 2-1. OPERATING DATA ANALYZER

All controls and indicators used during normal operation of the Data Analyzer are located on the top panel, and

input signal connections are made at the front panel (fig. 2-1). Fuses are located on the bottom of the unit.

Table 2-1. Controls, Indicators, Jacks, Fuses

| Control, Indicator              |                                                                                                                                                                                                                                 |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jack or Fuse                    | Function                                                                                                                                                                                                                        |

| DATA MARK                       | Lights when Mark signal is received.                                                                                                                                                                                            |

| indicator lamp                  |                                                                                                                                                                                                                                 |

| PWR switch                      | When pressed, applies power to Distortion Analyzer.                                                                                                                                                                             |

| INPUT switches                  |                                                                                                                                                                                                                                 |

| NEUTRAL                         | Condition Data Analyzer to monitor:                                                                                                                                                                                             |

| 20MA                            | 20ma neutral loop inputs.                                                                                                                                                                                                       |

| 60MA                            | 60ma neutral loop inputs.                                                                                                                                                                                                       |

| POLAR                           | Conditions Data Analyzer to monitor high-level (10 to 30ma) or low-level (+ 3 to x 25 volts) polar in-<br>put. (High- or low-level determined by front-panel jack connection.)                                                  |

| POLARITY REV switch             | Up (i.e., not pressed) position conditions Data Analyzer for positive Mark polar inputs and positive tip neutral inputs. When pressed, conditions Data Analyzer for negative Mark polar inputs and negative tip neutral inputs. |

| DISTORTION MODE                 | Select simultaneous:                                                                                                                                                                                                            |

| switches                        |                                                                                                                                                                                                                                 |

| BIAS<br>PEAK                    | Average bias distortion and total peak distortion (bias or end, whichever is higher) readouts for dis-<br>play on PERCENT DISTORTION indicator.                                                                                 |

| END                             | Average end distortion and total peak distortion (bias or end, whichever is higher) readouts for dis-                                                                                                                           |

| PEAK                            | play on PERCENT DISTORTION indicator.                                                                                                                                                                                           |

| RATE switches (four)            | Each selects specified baud-rate, according to signal being monitored.                                                                                                                                                          |

| CODE switches:                  | Condition Data Analyzer to monitor:                                                                                                                                                                                             |

| 5 LEV                           | 5-level code inputs.                                                                                                                                                                                                            |

| 8 LEV (or 7 LEV)                | 8-level or 7-level code inputs (whichever is established by strap option).                                                                                                                                                      |

| PARITY ERROR                    | Performs two functions:                                                                                                                                                                                                         |

| -                               |                                                                                                                                                                                                                                 |

| indicator lamp                  | <ul> <li>Lights to indicate parity error in 8-level or 7-level character; is extinguished when RESET<br/>switch is pressed and released.</li> </ul>                                                                             |

|                                 |                                                                                                                                                                                                                                 |

|                                 | <li>b. Lights brightly, when RESET switch is pressed and held, if battery has at least 0.5 operating</li>                                                                                                                       |

|                                 | hour remaining, thus indicating condition of internal battery.                                                                                                                                                                  |

| RESET <u>PEAK</u>               | Performs three functions:                                                                                                                                                                                                       |

| switch PARITY                   | a. Press-and-release resets peak distortion readout on PERCENT DISTORTION indicator; press-                                                                                                                                     |

|                                 | and-hold displays average distortion only.                                                                                                                                                                                      |

|                                 | b. Press-and-release, when PARITY ERROR lamp is lighted, extinguishes lamp.                                                                                                                                                     |

|                                 | c. Press-and-hold, in conjunction with PARITY ERROR lamp, indicates condition of internal bat-                                                                                                                                  |

| DEDOENT                         | tery.                                                                                                                                                                                                                           |

| PERCENT                         | Solid-state meter containing 16 LEDs, any two of which simultaneously indicate average and total                                                                                                                                |

| DISTORTION                      | peak distortion. Readouts are in increments of 3-1/3 per cent, from 0 to 50.                                                                                                                                                    |

| indicator                       |                                                                                                                                                                                                                                 |

|                                 | of Lights to indicate average Marking distortion condition; used with DISTORTION MODE switches                                                                                                                                  |

| indicator)                      | N to indicate average Marking bias or average Marking end distortion.                                                                                                                                                           |

| S indicator lamp (part of       | Lights to indicate average Spacing distortion condition; used with DISTORTION MODE switches to                                                                                                                                  |

| PERCENT DISTORTIO<br>indicator) | N indicate average Spacing bias or average Spacing end distortion.                                                                                                                                                              |

| LOW LEVEL (SIG                  | Provide input connections for low-level input signal.                                                                                                                                                                           |

| and GND) jacks                  |                                                                                                                                                                                                                                 |

| HI LEVEL LOOP jack              | Provides input connection for high-level polar (10 to 30ma) or neutral loop (20 or 60ma) input sig-<br>nals.                                                                                                                    |

| AC fuse                         | Fuses ac power line.                                                                                                                                                                                                            |

| I P fuse                        | Fuses at power line.<br>Fuses high-level (polar and neutral loop) input signal line.                                                                                                                                            |

|                                 | EUSES UIQUEIEVELUQUAL AUQ TEURALIQUUT UIQUE SIQUALITUE                                                                                                                                                                          |

#### 2-2. PRELIMINARY SETUP

The general procedure for setting up the Data Analyzer before operating the unit is described below:

a. Make certain that the correct internal strapping connections have been made for the given application.

b. Determine whether the mode of operation will be ac or battery.

(1) For the ac mode, connect the ac line cord to a 115- or 230-volt (as required), 60-Hz power source.

(2) For battery mode, check the condition of the internal battery by pressing the RESET switch and observing the PARITY ERROR indicator lamp. Use the chart below as a guide to determine whether the battery's condition will permit battery operation.

| Indicator Lamp<br>Intensity Level | Battery Condition                   |

|-----------------------------------|-------------------------------------|

| Dark (lamp                        | Completely discharged. Output volt- |

| does not light).                  | age too low to operate unit.        |

| Dim                               | Almost fully discharged. Battery    |

|                                   | should be recharged.                |

| Bright                            | Output voltage can operate unit for |

|                                   | at least 0.5 hour.                  |

|                                   |                                     |

#### 2-3. OPERATING PROCEDURES

After performing the preliminary setup, use the procedure outlined below as a guide for operating the Data Analyzer.

a. Select the type of loop circuit being monitored by pressing the appropriate INPUT switch. Three selections are available: NEUTRAL-20MA, NEUTRAL 60MA, or POLAR. The POLAR switch must be pressed for either high-level or low-level polar loop circuits.

b. If the input Marking signal is negative polar or negative tip neutral, press the INPUT-POLARITY REV switch. If the input Marking signal is positive polar or positive tip neutral, this switch need not be operated.

c. Make the proper input connections on the front panel (para 1-3b).

*d*. Select the baud-rate of the input signal by pressing the appropriate RATE switch.

e. Select the type of signal being monitored by pressing the appropriate CODE switch. Two selections are available: 5 LEV, and 8 LEV (or 7 LEV).

f. Determine the type of distortion analysis to be made by pressing either of two DISTORTION MODE switches:

(1) Selection of the BIAS/PEAK switch will provide indications of average percent bias distortion.

(2) Selection of the END/PEAK switch will provide indications of average percent end distortion.

#### NOTE

In both cases, total peak distortion indications (either bias or end, whichever is higher) are also provided at the same time.

g. Turn on the Data Analyzer by pressing the PWR switch. Check to see that the DATA MARK indicator

lamp:

(1) Blinks intermittently if a data pattern is being received.

(2) Remains ON if a steady Mark input is being received.

(3) Remains OFF if a steady Space input is being received.

h. Press RESET switch.

#### 2-4. INTERPRETING INDICATIONS

After the operating procedures described in paragraph 2-3 have been performed, percent and type distortion and parity-error incidence (7- or 8-level only) may be monitored.

a. Percent distortion presentation is available on the PERCENT DISTORTION display readout.

(1) If the DATA MARK indicator is not blinking (steady Mark or Space on the line), press the RESET switch; the PERCENT DISTORTION readout should indicate zero. If the DATA MARK indicator is blinking (data pattern being received) and distortion is present in the input signal, the PERCENT DISTORTION readout will provide one or two indications via the lighted red LEDs under the 0 to 50 PERCENT DISTORTION display scale (if two LED indications are presented, the lower one defines average distortion, and the higher defines peak distortion).

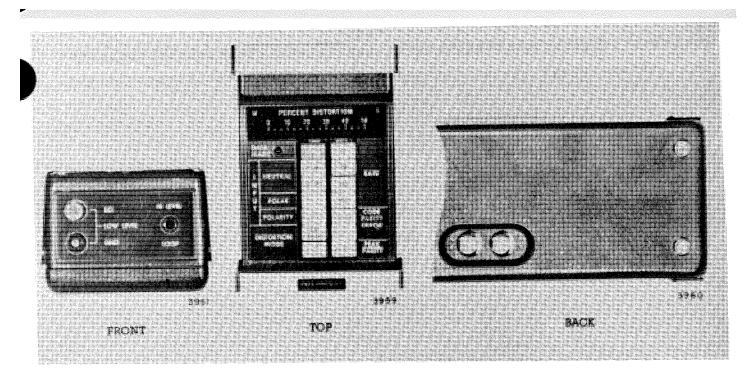

(2) Each graduation of the PERCENT DISTORTION scale represents 3-113 percent, + 1-213 percent. Thus, for example, a display as shown in figure 2-2 would indicate an average Marking bias (or end) distortion of 10 percent with a total peak distortion (bias or end) of 27 percent.

TYPICAL PERCENT DISTORTION READOUT

#### EL2PQO03

#### Figure 2-2. Typical Percent Distortion Readout.

b. Type of distortion present in the monitored signal is defined by the DISTORTION MODE switch that is pressed (i. e., bias distortion or end distortion).

(1) To further define the type of bias or end distortion present, two LED indicator lamps (M and S) are provided in the upper left-hand and right-hand corners, respectively, of the PERCENT DISTORTION display (fig. 2-2). If the BIAS/PEAK switch is pressed

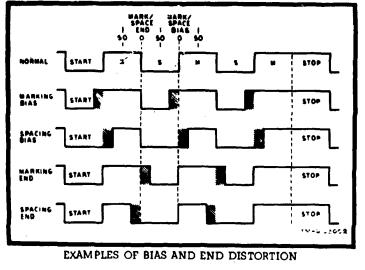

and the M indicator lamp is lighted, the PERCENT DISTORTION readouts represent the amount of average Marking bias and total peak distortion. If the END/PEAK switch is pressed and the M indicator lamp is lighted, the PERCENT DISTORTION readouts represent the average Marking end and total peak distortion. In either mode, the total peak distortion readout may be either bias or end, whichever is higher. A graphic representation of the different types of bias is shown in Note that total peak distortion is the figure 2-3. maximum excursion of any transition from nominal. For a complete analysis of the distortion present in the monitored signal, two readings should be made: one with the BIAS/PEAK switch pressed, and another with the END/PEAK switch pressed.

(2) Several peak distortion measurements should be made while analyzing a particular signal because one high peak reading may be only a random occurrence that does not represent the true peak distortion

over a period of time. Peak-reading samplings are effected by means of the RESET switch. Each time the switch is pressed and released, the peak distortion indication will be erased and the new peak distortion indication will appear. If the data signal being monitored contains a constant or unchanging amount of distortion, the bias/end and peak readings will be identical; thus, only one red LED indication will appear on the PERCENT DISTORTION readout. This condition may be observed when monitoring the output of a test pattern generator but would be unusual when used on a live data circuit.

c. Parity errors occurring in 7- or 8-level code inputs light the PARITY ERROR indicator lamp. Once lighted, the indicator is not extinguished until the RESET switch is pressed and released.

#### 2-5. OPERATIONAL CONDITION

After performing the operating procedures described in

paragraph 2-3, the Data Analyzer will be operational for the conditions established. With the unit connected to the particular type of data circuit for which it has been set up, the only change to be made on the operating Analyzer involves selection of either Distortion DISTORTION MODE switch (BIAS/PEAK or END/PEAK), and intermittent depression of the RESET pushbutton to reset the PARITY ERROR or percent peak distortion indications. During long periods of battery operation, occasionally check the condition of the battery, by means of the RESET switch and PARITY ERROR indicator, to insure optimum performance of the Data Analyzer.

#### 2-6. BATTERY CHARGING PROCEDURE

When fully charged, the battery can supply power to operate the unit continuously for approximately 12 hours. If the battery discharges completely, it can be brought to full charge in approximately 16 hours by turning the unit OFF and connecting the line cord to an ac outlet. Operation of the unit can be immediately restored, even when the battery has been completely discharged, by inserting the ac line cord into a power outlet. During this operational time, the internal battery receives a trickle charge which helps restore the battery and maintain it in a charged condition. After long periods of battery operation, the battery should be recharged to restore it to a fully charged condition.

#### CAUTION

DO NOT permit extensive periods of discharge, or the life of the battery will be reduced. To preserve battery charge, always turn OFF power when the unit is not in use.

EL2P0004

Figure 2-3. Examples of Bias and End Distortion

#### SECTION III

#### PRINCIPLES OF OPERATION

#### **3-1. OVERALL FUNCTIONAL DESCRIPTION**

Data Analyzer operation is described in the following paragraphs on an overall basis, using a block diagram to illustrate interrelationships of major functional sections. Most Data Analyzer circuits are unrepairable IC modules, therefore, details are provided only for circuits that contain discrete components.

#### 3-2. GENERAL

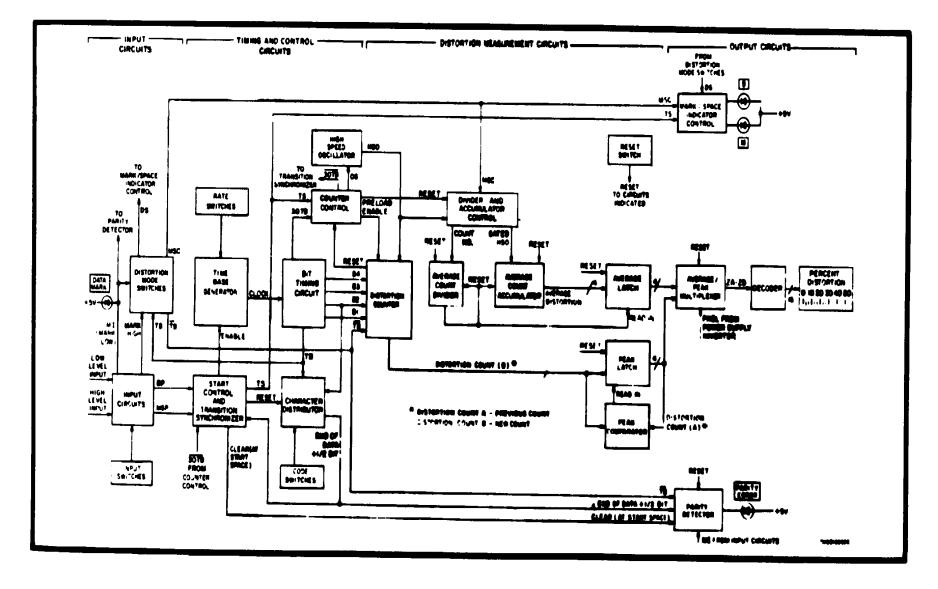

The Data Analyzer block diagram (fig. 3-1) shows major functional sections and principal control signals and data paths; power supply and switch control details are omitted for simplification Abbreviated signal names between functional blocks are the same as those shown on the schematic diagrams in the Maintenance section of this manual. As shown in the block diagram (fig. 2-4), the Data Analyzer comprises four major functional sections: input circuits, timing and control circuits, distortion measurement circuits, and output circuits.

a. The input circuit: provides the interface between the external polar or neutral input signal and the logic levels used in the Data Analyzer, and produces pulses that indicate the occurrence of every data-transition, and the beginning of a new character.

*b*. Pulses produced by the input circuits are used by the timing and control circuits to:

(1) Start the distortion count at the beginning of each character.

(2) Generate a time base for the selected baud-rate, which essentially divides each data-bit period into 30 increments (15 on either side of the center of a monitored data-bit). Each increment represents 3-1/3 percent distortion; thus, if data-bit transitions do not occur at the proper interval, the displacement from the normal transition point may be measured in increments of 3-1/3 percent distortion.

(3) Ensure that distortion measurements are made for the correct character-length (selected code) by disabling the timing and control circuit in the stop-Mark of the character; the circuit remains disabled until the beginning of the next character is detected.

c. The distortion measurement circuits:

(1) Count the total amount of distortion detected over a period of eight analyzed data-transitions, translate this total into an average count, and store the information (in BCD form) for subsequent display in the output circuits.

(2) Monitor the highest (peak) distortion count made, and store this information (in BCD form) for display in the output circuits.

*d*. The output circuits provide visual displays that indicate average and peak percent distortion, Marking or Spacing distortion, and parity error.

(1) Average and peak BCD values are multiplexed and decoded for simultaneous presentation on the PERCENT DISTORTION display.

(2) Using inputs from the timing and control and input circuits, the output circuit lights the M or S lamp to define the distortion present as Marking (lengthening of Mark-bits) or Spacing (lengthening of Space-bit), respectively.

(3) Parity-error indications are made on a character basis for 7- or 8-level codes; the parity error detector may be strapped for odd or even parity.

#### 3-3. INPUT CIRCUITS, FUNCTIONAL DESCRIPTION

Primarily, the input circuits which comprise discrete transistor circuits, IC modules, and associated switches convert all inputs (low-level polar, high-level polar, and 20ma or 60ma neutral) into 0-to-5 volt Mark/Space (MIS) and Space/Mark (SIM) transitions used by the timing and control circuits. INPUT switches NEUTRAL-20MA, -60MA, and POLAR insure that all signals applied to the input circuit are of the same voltage amplitude; INPUT-POLARITY REV converts negative polar Mark (negative tip-neutral) inputs into positive Mark signals, within the input circuit. Thus, the input circuit operates the same way regardless of the type of polarity of the input signal. The input circuits produce four output signals: MI (Mark Indicator), High Mark, BP (Bias Pulse), and MSP (Mark/Space Pulse).

a. MI performs several functions:

(1) Low when a Mark input is present, it lights the DATA MARK indicator lamp.

(2) Applied with the High Mark signal through a DISTORTION MODE switch, it generates an MSC (Mark]Space Control) signal as described below.

(3) It functions in parity detector operations as described in paragraph *3-6d.*

b. The High Mark and MI signals applied via the DISTORTION MODE switches generate the MSC signal used in the Mark/Space indicator control circuit (para 2-6c) and the distortion measurement circuit (para 3-5).

(1) With BIAS/PEAK pressed, the MSC signal is high for Mark.

(2) With END/PEAK pressed, the MSC signal is high for Space.

c. BP pulses, generated at each M/S and S/M transi

### EL2P0005

Figure 3-1. Data Analyzer, Block Diagram.

tion (see timing diagram (fig. 3-2)), function in the transition synchronization operation of the timing and control circuits as described below.

*d.* The MSP pulses (one produced at each inputsignal MIS transition), in conjunction with BP pulses, initiate operation of the timing and control circuit, as described in paragraph 3-4.

#### 3-4. TIMING AND CONTROL CIRCUITS, FUNCTIONAL DESCRIPTION

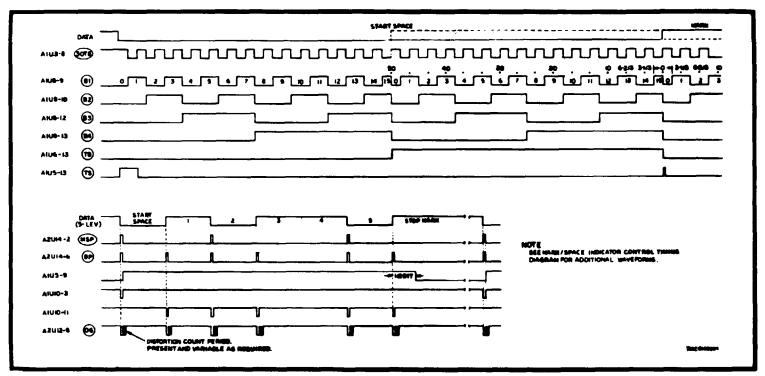

These circuits (start control and transition synchronizer, time base generator, bit timing circuit, counter control, high-speed oscillator, and character distributor) shown on the block diagram (fig. 3-1) generate all basic timing and control signals used in making average peak distortion measurements.

a. Start Control and Transition Synchronizer. This circuit, using MSP and BP pulses from the input circuits, produces several outputs. Its operation does not begin until one-half bit into the stop-Mark pulse, at which time it receives a reset pulse from the character distributor, enabling it for the next operation (MIS transition), and a reset pulse, re-applied to the character distributor, prepares the latter for the next bit-by-bit character count.

(1) When the next *MIS* transition of the monitored signal occurs, the MSP pulse from the input circuit triggers an output pulse from the start control and transition synchronizer, enabling the time base generator to produce a clock output upon which all distortion counts are based.

(2) As each subsequent M/S and SIM transition of the data-signal is received, BP pulses from the input circuit are applied to the start control and transition synchronizer. These pulses, combined with 30TB inputs from the counter control circuit, generate a TS (Transition Sync) pulse for the Mark/Space indicator control circuit and counter control circuit (operation of these circuits is explained in subsequent paragraphs).

b. Time Base Generator. The time base generator, comprising a free-running RC oscillator that drives a frequency countdown circuit, produces a highly stable clock-pulse output. Oscillator frequency is established by one of four RATE switches (top panel); the particular RATE switch that is pressed inserts a resistor of the proper value into the RC oscillator so that the output clock pulse is always 1/60 as wide as each data-bit being monitored. (Strapping options provided in the countdown circuit determined proper clock-pulse width [frequency] for the selected baud-rate). The time base generator is enabled on the first MIS transition (character-start) of the data-signal by an input from the start control and transition synchronizer; this enabling input is removed one-half bit into the stop-Mark pulse.

*c. Bit Timing Circuit.* This circuit, clocked by the time base generator, generates six frequency-stable outputs that represent most of the timing and gating signals used

by the distortion counter and control circuits. Functioning essentially as a frequency divider, the bit timing circuit provides 30TB, B1, B2, B3, B4, and TB (bit timing) outputs at the correct frequency for the selected baudrate. As shown in the timing diagram (fig. 3-2), these outputs represent 1160, 1132, 1116, 118, 1/4, and 1/2, respectively, of a data-bit width. (Note that, due to an internal reset function, B1, B2, and B3 are asymmetrical at the data-bit transition points and at the half-way point through each data-bit.) The TB pulse, used directly by the character distributor circuit as described in paragraph 3-4f, is coupled through an inverter in the DISTORTION MODE switch circuit and applied as t to the parity detector and distortion counter circuits (para 3-5a). The 30TB output, with the TS output of the start control and transition synchronizer, is applied to enable operation of the counter control circuit.

*d. Counter Control.* Simultaneous application of a TS pulse from the start 'control and transition synchronizer and a 30TB pulse from the bit timing circuit ensures that operation of the counter control begins on each transition of every data-bit. On receiving the TS and 30TB pulses, the counter control generates a Preload Enable signal for the distortion counter; an OG (Oscillator Gate) signal; an enable signal for a peak (distortion) comparator; and an inhibit signal for a divider and accumulator control.

(1) The Preload Enable signal allows bit timing pulses B1, B2, B3, B4, and TB (corresponding to a binary value between 0 and 15) to be preloaded into the distortion counter. This number represents the interval between data-transitions measured in fifteenths, with each fifteenth equaling 3-1/3 percent distortion (+ 1-2/3 percent). Thus, if the number 15 is preloaded, the counter will be full, indicating that less than 1-2/3 percent distortion is present. Preloading number 12 means that the interval between transitions is three counts short (i.e., that 10 + 1-2/3 percent distortion is present). For details see the description of the distortion counter (para 3-5a).

(2) As the Preload Enable signal is generated, the counter control also outputs an OG pulse that gates ON a high-speed oscillator. This action produces an output that causes the distortion counter to count up to 15 from the preloaded value.

(3) The peak comparator enable signal and the inhibit signal for the divider and accumulator control are both the complement of the OG pulse. The former is functional when at a high (logic 1) level; the latter when at a low (logic 0) level.

(a) When a data-bit transition occurs, the enable signal to the peak comparator is high, allowing the peak comparator to check the new distortion count

DATA ANALYZER, TIMING DIAGRAM

EL2P0006

Figure 3-2. Data Analyzer, Timing Diagram.

against the previous one and thereby update its information so that the highest (peak) value distortion count is available for display. After counting to 15, the distortion counter applies a reset pulse to the counter control; thus the peak comparator enable signal goes low (logic 0) to disable peak comparator output until the next data-bit transition, whereupon the sequence is repeated.

(b) While the peak comparator enable signal is low, the divider and accumulator inhibit input is also low (since both are the complement of OG); the HSO and MSC inputs to the divider and accumulator control are thus prevented from being used to generate count number and gated HSO outputs for the average count divider and accumulator circuits, respectively. When the divider and accumulator inhibit input is high (from databit transition until distortion counter completes count), the divider and accumulator is permitted to output count number and gated HSO pulse. (For details, see description of the distortion measurement circuits (para 3-5)).

e. High-Speed Oscillator. Using an RC oscillator almost identical to that in the time base generator, the high-speed oscillator produces a clock frequency output (HSO) of approximately 70kHz. The oscillator is gated ON by an OG input from the counter control, which occurs at each transition of the monitored data input. The resultant outputs clock the distortion counter and average count accumulator in the distortion When the distortion counter measurement circuits. control reaches its maximum count (15), it resets the counter which, in turn, inhibits the OG signal and thereby disables the high-speed oscillator.

f. Character Distributor. Essentially a binary counter (with a NAND gate output) controlled by the 'selected top-panel CODE switch (5 LEV, and 8 LEV or

7 LEV), the character distributor insures that distortion measurements and parity error detection occur for the correct number of data-bits in the selected code (i.e., for the correct character-length).

(1) Initially turned ON at the beginning of a character (by a reset pulse from the start control and transition synchronizer), the character distributor counts data-bits, using TB as the counter input. By means of internal strapping and connections through the selected CODE switch, counter output is NANDed with TB and B2 to produce a pulse one-half a bit time after occurrence of the last data-bit in the character (one-half a bit into stop-Mark). Thus, for example, if a 5-level code is selected. the end-of-character pulse from the character distributor will occur 6-1/2 bit-times after the beginning of the start-Space bit (start-Space plus 5 data-bits, plus one-half bit). This output is reapplied to the start control and transition synchronizer, stopping operation of that circuit until the next M/S transition (beginning of new character) occurs, causing the entire cycle to be repeated.

(2) The end-of-character pulse also enables the parity detector to output a signal indicating whether or not a parity error was detected during that character.

#### 3-5. DISTORTION, MEASUREMENT CIRCUITS, FUNCTIONAL DESCRIPTION

The Data Analyzer distortion measurement circuits comprise a distortion counter, divider and accumulator control, average count accumulator, average count divider, average latch, peak latch, and peak comparator, as shown in the block diagram (fig. 2-4). Using inputs from the timing and control circuits, the distortion measurement circuits produce two 4-bit binary outputs representing the average and peak distortion present in the monitored data-signal.

a. Distortion Counter. The distortion counter (four exclusive OR gates, four NAND gates, and a 4-stage counter) provides a binary output, the value of which represents the difference in time between the point when a data-bit transition should normally occur (per the selected baud-rate) and the point at which it actually occurs in a monitored data-bit. Inputs B1, B2, B3, B4, and TB establish the point at which the transition should normally occur.

(1) As shown in the timing diagram (fig. 2-5), zero distortion is present only when B1 through B4 are all high and TB is-low, or vice versa. For various values of distortion, B1 through B4 provide different logic-l/logic-0 combinations; TB is a logic 1 for the first half of the normal bit-time (Spacing bias or Marking end) and a logic 0 for the second half of the normal bit-time (Marking bias or Spacing end). Each resulting logic-0/logic-1 combination, representing B1 through B4 and TB, preloads the 4-stage counter with a particular binary value whenever a transition occurs in the monitored data-bit.

(2) When a data-bit transition is sensed, a preload enable pulse is applied from the counter control circuit to the distortion counter. Consequently, the 4-bit binary value established by the logic levels of B1 through B4 and TB, at the moment of transition, are preloaded into the 4-stage counter. A value of 15 (binary 1111), representing less than 1-2/3 per cent distortion, is the highest number that can be preloaded into, or counted by, the counter since it contains only four stages. Any other preloaded number indicates the presence of distortion. The quantity of distortion is equal to the difference in count between 15 and the preloaded number, with each count representing 3-1/3 percent distortion, + 1-2/3 percent. Thus, for example, a preloaded 12 indicates a difference of three counts, or 10,  $\pm$  1-2/3 percent distortion.

(3) The counter counts up from the preloaded value to 15 triggered by HSO clock pulses from the

high-speed oscillator. As described in paragraph 2-4e, the oscillator is enabled by an OG output from the counter control at the same time that the counter control provides the preload enable signal to the distortion counter. This count-up value (the complement of the preloaded value, with respect to 15), representing the percent distortion measured for a particular data-bit, is applied from the distortion counter to a peak latch and peak comparator as a 4-bit parallel binary number (count (B)). When the counter reaches the maximum count of 15, it outputs a reset pulse to the counter control, removing the preload enable and OG signals and thereby inhibiting the distortion counter.

(4) The above sequence is repeated on the next data-bit transition when the TS and 30TB inputs again cause the counter control to generate preload enable and OG outputs.

*b. Divider and Accumulator Control.* This circuit is enabled at each transition of a monitored data-bit, by application of HSO clock pulses from the high-speed oscillator; simultaneously, MSC inputs are provided from the input circuits via the selected DISTORTION MODE switch.

(1) Except that its amplitude is limited to 5 volts, the MSC input is a replica of the actual monitored data signal. The MSC signal may, however, assume one of two polarities, depending on which DISTORTION MODE switch is pressed. With BIAS/PEAK pressed, the Mark signal is positive; with END/PEAK pressed, the Space signal is positive. It is the positive portion of the MSC signal, in conjunction with the HSO input, that activates the divider and accumulator control. The selected MSC signal insures that bias distortion measurements will be made with respect to S*IM* transitions and that end distortion measurements will be made with respect to M/S transitions (both transitions being positive, as selected by the appropriate DISTORTION MODE switch).

(2) With MSC and HSO inputs present, the divider and accumulator control provides two outputs: count No., which is applied to the average count divider; and gated HSO, which is applied to the average count accumulator. These outputs are present until the distortion counter (para 3-5a) reaches its maximum count, at which time it outputs a reset pulse to the counter control circuit; the latter, in turn, applies an inhibit pulse to the divider and accumulator control. With this arrangement, the number of grated HSO pulses applied to the average count accumulator is the same as that applied to the distortion counter (with each pulse representing 3-1/2 percent,  $\pm$  1-2/3 per cent distortion). The count No. output to the average count accumulator represents the number of transitions (M/S or SIM) in the monitored data.

*c.* Average Count Accumulator. A 7-stage counter, this circuit stores the gated HSO count over a period of eight data-bits (controlled by the average count divider

described below). Each HSO count represents 3-1/3 + 1-2/3 percent distortion; therefore, the 7-stage counter stores the average distortion measured for a nominal character length.

(1) If maximum distortion (50 percent were present in each monitored data-bit, 15 HSO pulses would be loaded into the counter 8 times, for a total count of 120. Likewise, if only 3 percent distortion were present in each data-bit, 1 HSO pulse would be loaded into the counter 8 times, for a total count of 8. Other values of percent distortion in each data-bit would produce proportionate counts between 8 and 120.

(2) Only values between 8 and 120 have any significance; therefore, only the last four stages of the counter (decimal 8, 16, 32, and 64) are used. These outputs are equivalent to BCD values of 1, 2, 4, and 8, respectively. Sixteen possible logic-0/logic-1 combinations of these four outputs represent the average distortion measured for a particular character. Based on the previous examples: with 50 percent distortion, all four outputs would be logic 1 (decimal 15); with 3 percent distortion, the 8-count output would be logic 1 and the other three-outputs would be logic 0 (decimal 1).

(3) The four BCD output lines are applied to the average latch, which is controlled by the average count divider.

*d.* Average Count Divider. This circuit counts transitions of the monitored data-signal. After counting eight transitions, it resets itself, resets the average count accumulator, and provides a read-in signal to the average latch. In resetting itself and the average count accumulator, the average count divider effectively ends the period of one distortion measurement and allows the next period of measurement to begin.

(1) The selected measurement period (eight data transitions) represents a compromise that provides an average distortion count from a maximum of eight characters (one transition per character) to a minimum of two to three characters (three MIS or SIM transitions per 5-level character, or five M/S or SIM transitions per 8-level character). A longer period of integration would slow the response such that wide variations in distortion would be lost; only a long-term average, providing a less true representation, would thus be seen. If a shorter period were used, the distortion indication might change so rapidly that it would be useless.

(2) The read-in signal applied to the average latch allows the average distortion measurement at the input of the average latch to be transferred to the output side.

*e. Average Latch.* A storage device, the average latch receives four BCD inputs (from the average count accumulator) representing average distortion.

These inputs, constantly updated during the 8-transition measurement interval, are held in storage until the eighth data-transition occurs, at which time a read in signal is applied from the average count divider This signal enables the average latch to transfer the four stored logic bits to an average/peak multiplexer is the output circuit.

f. Peak Latch and Peak Comparator. The peak latch is identical with the average latch described in e above except that the peak latch operates in a slightly different way, under control of a peak comparator.

(1) The peak latch and peak comparator both receive four parallel logic inputs (count B) from the distortion counter; these inputs represent, in binary form, the distortion measured for a particular data-bit Count B (referred to as the new count) is compared by the peak comparator with the four logic bits, count A (referred to as the previous count), on the output side of the peak This comparison takes place on each datalatch. transition, when the counter control applies an enable signal to the peak comparator. If the previous count is less than the new count, the peak comparator provides a read-in signal to enable the peak latch t( transfer the new count to the average/peak multiplexer in the output circuit. With a new count appearing on the output side of the peak latch, both inputs to the peak comparator become equal and the read-in signal to the peak latch is disabled.

(2) The condition in (1) above is maintained until the peak latch input again exceeds the output, causing the sequence to be repeated. As a result, the peal (highest) distortion value is always presented to' the average/peak multiplexer.

#### 3-6. OUTPUT CIRCUITS, FUNCTIONAL DESCRIPTION

Comprising an average/peak multiplexer, a decoder the PERCENT DISTORTION display, Mark/Space indicator

control, and parity detector, the output circuits provide the visual display that indicates: average and peak distortion; type (Marking or Spacing) of distortion; and parity errors in 7- or 8-level codes.

a. Average/Peak Multiplexer. The average/peak multiplexer (essentially, four pairs of AND gates, each pair driving an inverter output through a NOR gate) combines detected average and peak distortion, on a time-sharing basis, for simultaneous presentation on the PERCENT DISTORTION display. Four identical circuits are required, because the average and peak torsion outputs from the respective latching circuits are each represented by four binary logic bits.

(1) One AND gate of each pair receives a logic input from the average latch; the other AND gate, a logic input from the peak latch. However, only one AND gate in each of the four pairs is enabled at one time, by a 50kHz Peak Blanking (PKBL) pulse from a free-running multivibrator in the power supply inverter (para 3-8).

(2) Resultant output from the multiplexer (Za-Zd), a rapid alternation of four binary logic bits representing average and then peak distortion, is applied to a decoder.

*b.* Decorder. The decoder is basically a 4-by-16 matrix that converts the four alternating, binary coded, average/peak bits into a decimal output on 16 lines. The lines are connected to the 16 LEDs that produce the PERCENT DISTORTION display. Because of the rapid alternation of the average and peak distortion inputs, the displays appear to be simultaneous, but they are actually being turned ON and OFF at a 50kHZ rate. The chart below lists the 16 possible logic inputs and the resultant percent distortion display.

| DECODER INPUT    |                |                |     |            |                   |     |            |     | <u>T_</u> |

|------------------|----------------|----------------|-----|------------|-------------------|-----|------------|-----|-----------|

|                  |                |                |     | PERCENT*   |                   |     |            |     | PERCENT*. |

| ZD               | Z <sub>C</sub> | Ζ <sub>B</sub> | ZA  | DISTORTION | $Z_D Z_C Z_B Z_A$ |     | DISTORTION |     |           |

| (8)              | (4)            | (2)            | (1) | (±1-213)   | (8)               | (4) | (2)        | (1) | (+ 1-2/3) |

| 0                | 0              | 0              | 0   | 0          | 1                 | 0   | 0          | 0   | 26-213    |

| 0                | 0              | 0              | 1   | 3-113      | 1                 | 0   | 0          | 1   | 30        |

| 0                | 0              | 1              | 0   | 6-2/3      | 1                 | 0   | 1          | 0   | 33-1/3    |

| 0                | 0              | 1              | 1   | 10         |                   | 1   | 0          | 1   | 1 36-2/3  |

| 0                | 1              | 0              | 0   | 13-1/3     | 1                 | 1   | 0          | 0   | 40        |

| 0                | 1              | 0              | 1   | 16-2/3     | 1                 | 1   | 0          | 1   | 43-1/3    |

| 0                | 1              | 1              | 0   | 20         | 1                 | 1   | 1          | 0   | 46-2/3    |

| 0                | 1              | 1              | 1   | 23-1/3     | 1                 | 1   | 1          | 1   | 50        |

| *Average or peak |                |                |     |            | I                 |     | 1          | I   |           |

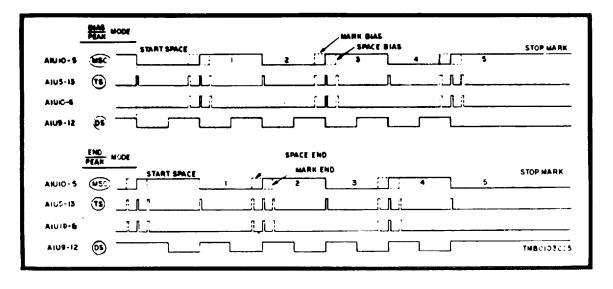

*c. Mark/Space Indicator Control.* Comprising a NAND gate, inverter, and flip-flop, this circuit controls the lighting of the M and S LEDs (in the PERCENT DISTORTION display) which whether the percent distortion displayed represents Mark or Space distortion. The control circuit uses the DS and MSC inputs from the DISTORTION MODE switches, and TS provided form the start control and transition synchronizer.

(1) As explained in paragraph 2-5b(1), polarity of the MSC signal depends on which DISTORTION MODE switch is pressed (if BIAS/PEAK is pressed, the Mark signal is positive; if END/PEAK is pressed, the Space signal is positive). Likewise, the DS signal (derived from TB) is a logic 1 during the *second* half of each data-bit if BIAS/PEAK is pressed, and a logic 1 on the *first* half of each data-bit if END/PEAK is pressed. The TS pulse occurs on each M/S or S/M transition of the monitored data.

(2) As shown in the timing diagram (fig. 2-6), if the SIM transition occurs too early in BIAS/PEAK operation, the TS pulse is positive while DS is positive, lighting the M lamp to indicate Marking bias. Similarly, if the SIM transition occurs too late, the TS pulse is positive when the DS pulse is *negative*, lighting the S lamp to indicate Spacing bias.

(3) In END/PEAK operation, the action is essentially identical, except that M/S transitions control lighting of the M or S lamp.

*d. Parity Detector.* The parity detector provides a PARITY ERROR indication, on a character-basis, in either 7- or 8-level code operation; a strapping option enables detection of either odd- or even-parity errors.

(1) Four inputs are supplied to the parity detector: clear, end-of-data plus 1/2 bit, MI, and TB. The clear input resets the circuit at the beginning of each character's start-Space. With the circuit initially cleared, MI and TB inputs are then used in the actual parity error detection.

(2) MI is a logic 1 for each Space bit appearing in the monitored data. The TB input is differentiated so that it produces a pulse in the middle of each data-bit period whether or not any MIS or SIM transition has occurred (e.g., the input data may remain in a Space condition for three bit periods, but this would still produce three differentiated TB pulses). The MI and TB inputs are used to count the number of Space bit-periods in the monitored data, by alternately setting and resetting a flipflop for each such period. If the circuit is strapped for even polarity and an even number of Space bit-periods are counted, a parity error is indicated. If strapped for odd parity and an odd number of Space bit-periods are counted, a parity error is also indicated.

(3) The parity detector output is not enabled until an end-of-data plus 1/2 bit signal is received from the character distributor. If a parity error has been detected, the parity detector outputs a logic 0, lighting the

PARITY ERROR lamp; the lamp remains lighted until the RESET pushbutton is pressed and released.

#### 3-7. DISCRETE COMPONENT CIRCUITS-DETAILED DESCRIPTIONS

INPUT INTERFACE (fig. FO-1) circuit comprising transistors Q1 and Q2, and three inverters which are part of IC U14, converts all types of inputs to logic levels of 0 and + 5 volts and generates the MI, MSP, and BP signals used in the Data Analyzer.

a. All Data Analyzer inputs are converted to 6-volt pulses at the C11R14 junction.

(1) Low-level polar (positive Mark) signals are normally at this amplitude; therefore, they require no conversion and are applied directly to the junction through R12 and S5A.

(2) In high-level polar (nominally 20ma) or 20ma neutral operation, the 20ma input is converted to 6 volts across R24 (with applicable switch S2 or S4 pressed) and applied to the junction through R13.

(3) For 60ma neutral operation, with S3 pressed, the input is converted to 6 volts across R25, and is applied to the junction through R13.

b. C11/14 function as an integrator to filter out transients present in the input; the resulting signal is applied to the base of amplifier Q1 across diodes CR1-CR2 which, in polar operation, are referenced to 4.3 volts established by Zener diode VR2. This 4.3-volt dc level also serves as the return reference for the external + 6-volt polar input (via REV switch S5) so that *M*IS inputs actually vary between 10.3 and - 1.7 volts.

(1) However in polar operation, CR1-CR2 limit the Q1 base signal input to voltage swings between approximately 3.6 and 5 volts. With the Q1 emitter referenced to approximately 5 volts by VR2, CR3, and R17, Q1 is cut off when the base input rises above 4.3 volts (Mark). As the input drops below 4.3 volts (Space), Q1 is driven into conduction. Output form the Q1 collector is a negative Mark (ground) and a positive Space (5 volts).

(2) Neutral operation is essentially the same as polar, except that, for neutral signals, common return is referenced to ground through R2-R21 and S4A; R2-R21 provide half-current slicing to establish a 3volt Mark/Space switchover reference.

#### NOTE

With negative Mark low-level polar (or negative-tip high-level polar/neutral inputs), REV switch S5 is pressed and input signals are applied to the emitter of Q1, producing ground/5-volt outputs at the Q1 collector.

c. Outputs from Q1 are applied to the base of switch Q2. With a ground (Mark) input, the Q2 collector is at 10 volts; with a 5-volt (Space) input, the collector is at

MARK/SPACE INDICATOR CONTROL, TIMING DIAGRAM

EL2PQ007

0 volt. The collector output is: coupled back to the Q1 base through hysteresis feedback resistor R16, to provide greater noise immunity; and applied to inverter input U14-3 and differentiator C7-R22. The inverted output (negative Mark) from U14-4 (MI) is fed to differentiator C6-R20, whereas the positive Mark signal appears at C7-R22. MI, which lights the DATA MARK lamp (indicating presence of a positive Mark input) is used in the Data Analyzer parity detector circuit as described in paragraph 3-6d.

*d*. Differentiator action is the same for both types of circuits, except that the circuits operate on signals of opposite polarity.

(1) Output of C6-R20 is a sharp negative pulse for each AIM transition and a sharp positive pulse for each MIS transition. The positive pulse is blocked by CR4 (part of 2-input OR gate CR4-CR5), but the negative input is coupled to inverter input U14-5.

(2) Output of C7-R22 is a positive pulse for each S/M transition and a negative pulse for each *MIS* transition. The positive pulse is blocked by CR5 so that only the negative pulse is applied to U14-5. The resultant inverted output at U14-6 is a stream of positive pulses representing M/S and SIM transitions of the input data. This BP signal is used in the Data Analyzer timing and control circuits as described in paragraph 3-4.

e. The differentiated output from C7-R22 is also applied to inverter input U14-1. Since the U14-1 input is normally held at + 5 volts, applied through R22, only the negative-going pulse has any effect, producing a positive pulse at U14-2. Representing M/S transitions of the input data, this pulse (designated "MSP') is used in the Data Analyzer timing and control circuits as described in paragraph 3-4.

#### 3-8. POWER SUPPLY INVERTER (fig. FO-1)